Breaking News

UN IPCC climate group reverses course on doomsday predictions...

UN IPCC climate group reverses course on doomsday predictions...

False Flag Alert! U.S. Intelligence Claims Cuba Considering Drone Strike On Key West Florida...

False Flag Alert! U.S. Intelligence Claims Cuba Considering Drone Strike On Key West Florida...

Exclusive -- Robert F. Kennedy Jr.: Biden Admin's 453 Pages of Food Guidelines...

Exclusive -- Robert F. Kennedy Jr.: Biden Admin's 453 Pages of Food Guidelines...

Comedian replacing Stephen Colbert appears to take a swipe at his predecessor as he vows...

Comedian replacing Stephen Colbert appears to take a swipe at his predecessor as he vows...

Top Tech News

Sodium Ion Batteries Can Reach 100 Gigawatt Per Hour Per Year Scale in 2027

Sodium Ion Batteries Can Reach 100 Gigawatt Per Hour Per Year Scale in 2027

Juiced Bikes proves capable electric motorcycles don't have to cost a lot

Juiced Bikes proves capable electric motorcycles don't have to cost a lot

Headlight projectors turn your car into a drive-in theater

Headlight projectors turn your car into a drive-in theater

US To Develop Small Modular Nuclear Reactors For Commercial Shipping

US To Develop Small Modular Nuclear Reactors For Commercial Shipping

New York Mandates Kill Switch and Surveillance Software in Your 3D Printer ...

New York Mandates Kill Switch and Surveillance Software in Your 3D Printer ...

Cameco Sees As Many As 20 AP1000 Nuclear Reactors On The Horizon

Cameco Sees As Many As 20 AP1000 Nuclear Reactors On The Horizon

His grandparents had heart disease.

At 11, Laurent Simons decided he wanted to fight aging.

His grandparents had heart disease.

At 11, Laurent Simons decided he wanted to fight aging.

Mayo Clinic's AI Can Detect Pancreatic Cancer up to 3 Years Before Diagnosis–When Treatment...

Mayo Clinic's AI Can Detect Pancreatic Cancer up to 3 Years Before Diagnosis–When Treatment...

A multi-terrain robot from China is going viral, not because of raw speed or power...

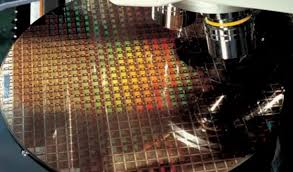

Taiwan Semiconductor Will Have Volume Production of 3 Nanometer Chips in 2022

TSMC was the first company to use ASML's EUV lithography machines for high-volume production and now has at least three processes that use EUV for select layers. They use EUV lithography for its N7+, N6, and N5 nodes.

TSMC's 2nd generation 7 nm technology (N7+) uses EUV for up to four layers in order to reduce its use of multi-patterning techniques when building highly complex circuits. The 6 nm process (N6) is for customers to re-use IP designed for 1st generation 7 nm, per the report. TSMC's 5 nm process (N5) can use EUV for up to 14 layers. 5nm has significant increase in transistor density and performance enhancements.

2nd generation 5 nm (N5P) and 4 nm (N4) fabrication processes are based 5 nm technology and will have performance and power benefits. N5P will be available in 2021. N4 chips will have volume production in 2022.

Next-generation 3 nm process (N3) will be a full node improvement over N5. N3 will have 70 percent logic density gain, 15-percent performance gain, and 30-percent power reduction over the 5-nm process. N3 will use EUV over 20 layers.

Nextbigfuture covered Taiwan Semiconductors plans from 2017. TSMC has kept on track with its Moore's Law roadmap to reach 3-nanometer chips by 2022.

The World's Biggest Fusion Reactor Just Hit A Milestone

The World's Biggest Fusion Reactor Just Hit A Milestone